## Satellite, Thermal Design for the MAX2116 and MAX2118

This application note provides thermal analysis for the MAX2116 and MAX2118 directconversion tuner ICs. Maximum ambient temperature is found to be 105°C. The thermal resistance from case to ambient is 66.3°C/Watt. Typical junction temperature is estimated as 56.2°C with a 25°C ambient.

Additional Information: <u>Wireless Product Line Page</u> <u>Quick View Data Sheet for the MAX2116, MAX2118</u> <u>Applications Technical Support</u>

#### Introduction

The MAX2116/MAX2118 use a 40 pin QFN thermally enhanced package. The exposed paddle makes this package a very effective thermal conductor, simplifying thermal design.

The majority of the heat travels through the exposed paddle. The leads and top of the package dissipate very little. Connecting the paddle to PCB copper provides a thermal path. More copper surface area provides better cooling.

The most effective way to promote cooling is to use topside copper under the exposed paddle. Due to layout constraints, this is often difficult to achieve. The next best method is to use vias under the exposed paddle connected to a solid piece of copper such as a ground plane. The MAX2116 EVkit is a good example of how this can be done using a two-layer board.

An application note that provides a good background on thermal issues is "<u>Thermal</u> <u>Considerations of QFN and Other Exposed-Paddle Packages</u>."

### Definitions

Tj = Junction temperature in °C. Tc = Case temperature in °C. The case temperature is taken at the center of the exposed paddle located on the bottom of the QFN package.

Ta = Ambient temperature in °C i.e., temperature of the air surrounding the IC.

Tja = Tj - Ta = Temperature drop from junction to ambient in °C.Tjc = Tj - Tc = Temperature drop from junction to case in °C.Tca = Tc - Ta = Temperature drop from case to ambient in °C.

Pd = Power dissipated in the IC.

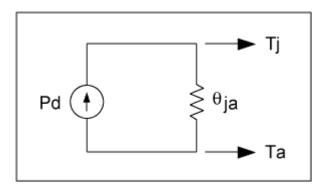

Figure 1. Basic thermal model

Power can be modeled as a current, thermal resistance can be modeled as a resistance and temperature can be modeled as a voltage (See Figure 1). Inspection of Figure 1:

• ja is a measure of thermal resistance measured in °C/W. Small numbers for • ja are desirable. Inspection of Figure 1 and EQN2 shows low values of ja will produce low temperature drop Tja for a given power Pd. By minimizing temperature drop the designer is able to maintain a low junction temperature for a fixed ambient temperature (EQN3).

| Tja = <b>⊕</b> ja • Pd           | EQN2 |

|----------------------------------|------|

| $Tj = Ta + \Theta ja \bullet Pd$ | EQN3 |

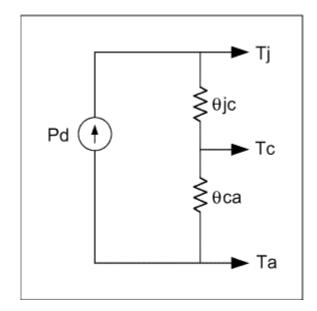

Figure 2. Detailed thermal model

Øja is the sum of Øjc and Øca (See Figure 2 and EQN 4). Øjc is set at 2 °C/W for the 40 pin QFN MAX2116/MAX2118. The designer does not have control over this parameter. The designer does have control over Øca.

$$\Theta ja = \Theta jc + \Theta ca$$

EQN4

#### Conditions

Tjmax = 150 °C

Pdmax = 1391mW, 5.25V, 265mA Pdnom = 975mW , 5.0V, 195mA

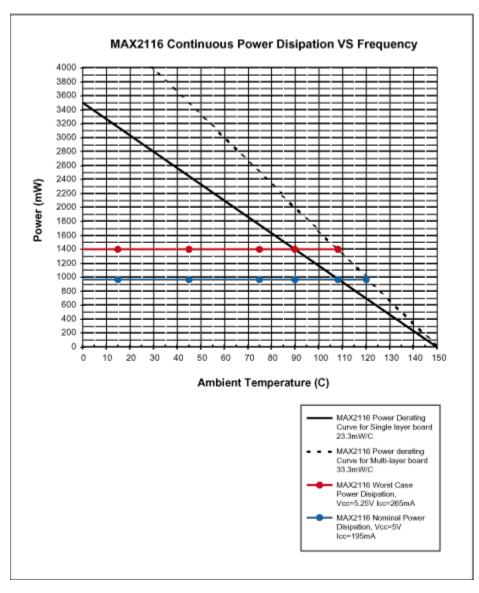

As can be observed above there are two numbers for @ja. Two PCB's have been manufactured and measure according to JDEC standards<sup>4</sup>. The single layer board shows a very conservative thermal resistance. In all reality it is possible to come closer to the multi-layer thermal resistance of  $@ja = 30 \degree$ C/W. Keep in mind the JDEC multi-layer board uses 2 oz. copper and 9 via under the exposed paddle. The typical two layer board will use 1oz copper and will probably have a thermal resistance slightly higher than 30 °C/W.

Figure 3. The MAX2116 continuous power derating curve

### Designs

Following are some general design guidelines for determining the thermal heat sink required.

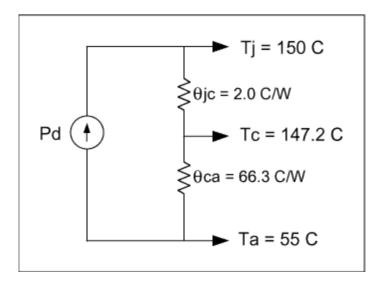

- 1. Determine maximum ambient temperature (Ta) the IC will encounter. Lets assume the maximum room temperature on top of a hot TV will be a balmy 49°C with a 6 °C heat rise from the circuitry. This would set the maximum ambient temperature to 55 °C.

- 2. Determine maximum junction temperature. For the MAX2116 and MAX2118 this is Tjmax =  $150 \text{ }^{\circ}\text{C}$ .

- Determine maximum power dissipation in the IC. According to the MAX2116/MAX2118 data sheet the maximum current is 265mA and the maximum supply voltage is 5.25V. Pdmax = 265mA • 5.25V = 1391mW

- 4. Calculate the total thermal resistance needed from junction to ambient (EQN1). If a = (Tj-Ta) / Pd = 95 °C / 1.391W = 68.3 °C/W. So a MAX2116/8 and PCB with a combined thermal resistance of 68.3 °C/W would be required.

- 5.  $\Theta ca = \Theta ja \Theta jc = 68.3 2 = 66.3 \text{ °C/W}$

- 6. A PCB design with at most  $@ca = 66.3 \degree C/W$  would be required.

#### Analysis

Lets calculate maximum ambient temperature for a typical design.

- 1. Lets assume a two layer board with 1oz copper has  $@ja = 32 \degree C/W$ .

- 2. Calculate maximum power. Pdmax = 265mA 5.25V = 1391mW

- 3. Calculate junction to ambient temperature drop. Tja =  $1.391W \cdot 32C/W = 44.51^{\circ}C$ .

- 4. Calculate maximum ambient temperature. Ta = Tj Tja =  $150C 44.51^{\circ}C = 105^{\circ}C$ .

Lets calculate typical junction temperature for nominal conditions

- 1. Lets assume a two layer board with 1oz copper has  $@ja = 32 \degree C/W$ .

- 2. Calculate nominal power. Pdnom =  $195mA \cdot 5.0V = 975mW$

- 3. Calculate junction to ambient temperature drop. Tja =  $0.975W \cdot 32C/W = 31.2$  °C.

- 4. Calculate junction temperature assuming Ta = 25 °C. Tj = Tja + Tja = 31.2 °C + 25 °C = 56.2 °C

# In The Lab

One way of measuring @ca would be to place a resistor on the exposed paddle land pattern on the PCB. Apply thermal grease to the resistor and pad so the heat flow is directed to the pad. Set a voltage across the resistor, which supplies a known power Pd. Measure the temperature (Ta) of the air with a thermocouple. Measure the temperature (Tc) of the PCB pad with a thermocouple. Get the thermocouple close to the center of the pad if possible. Make the measurement in an enclosed card board box to prevent air currents altering the results<sup>4</sup>.

## Notes:

1 Amkor Technology, Application Notes for Surface Mount Assembly of Amkor's Micro Lead Frame (MLF) Packages. Application Note, Amkor Technology, March 2001.

2 Guenin Bruce, What Are All these Different Thermal Numbers: Theta's, Psi's? A Minitutorial, Amkor Technology, February 1999.

3 Maxim Application Note, "<u>Thermal Considerations of QFN and Other Exposed-Paddle</u> <u>Packages</u>"

4 JESD51 Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device)

5 JESD51-7 High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

6 JESD51-9 Test Boards for Area Array Surface Mount Packages Thermal Measurements

### **MORE INFORMATION**

MAX2116: <u>QuickView</u> -- <u>Full (PDF) Data Sheet (320k)</u> MAX2118: <u>QuickView</u> -- <u>Full (PDF) Data Sheet (320k)</u>